Introduction: Why Changing Your Gmail Password Matters

In today’s digital landscape, our email accounts are gateways to a vast amount of personal information. From banking details to social media profiles, a compromised Gmail account can lead to significant security breaches and identity theft. Regularly changing your Gmail password is a crucial step in maintaining your online security and protecting your sensitive data. While forgetting your password can be a hassle, knowing how to change it using your old password is a straightforward process that can save you from potential security risks. This comprehensive guide will walk you through the steps to change your Gmail password using your existing password, ensuring your account remains secure and accessible.

We’ll cover everything from the initial steps of accessing your Google account settings to creating a strong, unique password that can withstand potential hacking attempts. Furthermore, we’ll delve into best practices for password management and additional security measures you can implement to fortify your Gmail account against unauthorized access. Whether you’re a seasoned tech user or new to the digital world, this guide will provide you with the knowledge and tools you need to confidently manage your Gmail password and safeguard your online identity.

Accessing Your Google Account Settings

The first step in changing your Gmail password is to access your Google Account settings. This can be done through your Gmail account or directly through your Google Account page. Here’s how to do it:

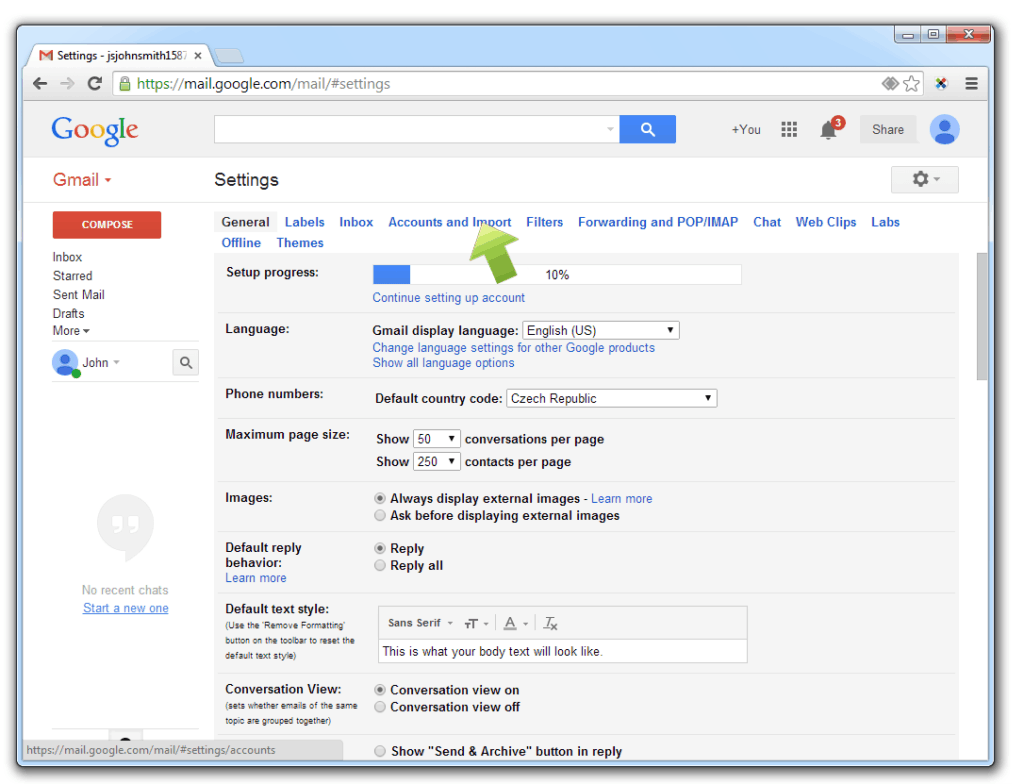

- Open your Gmail account: Go to mail.google.com and sign in with your current email address and password.

- Navigate to your Google Account: Once you’re logged in, click on your profile picture or initial in the top right corner of the screen. A dropdown menu will appear.

- Select “Manage your Google Account”: In the dropdown menu, click on the “Manage your Google Account” button. This will take you to your Google Account dashboard.

Alternatively, you can directly access your Google Account settings by going to myaccount.google.com and signing in.

Finding the Password Change Option

Once you’re in your Google Account settings, you need to find the option to change your password. Here’s how:

- Navigate to the “Security” section: On the left-hand side of the Google Account dashboard, you’ll see a navigation menu. Click on the “Security” option.

- Scroll down to “Signing in to Google”: In the Security section, scroll down until you find the “Signing in to Google” section.

- Select “Password”: Under the “Signing in to Google” section, you’ll see the “Password” option. Click on it. You may be asked to verify your identity by entering your current password.

If you have recently changed your password, it might take a few moments for the system to update. Be patient and try again in a few minutes if you encounter any issues.

Entering Your Current Password

Before you can change your Gmail password, Google requires you to verify your identity by entering your current password. This is a security measure to ensure that only the account owner can make changes to the password.

- Enter your current password: On the “Password” page, you’ll be prompted to enter your current password. Type it in carefully, making sure to avoid any typos.

- Click “Next”: Once you’ve entered your password, click the “Next” button. If you’ve entered the correct password, you’ll be taken to the password change screen.

If you’ve forgotten your password, you’ll need to go through the password recovery process. This guide focuses on changing your password when you know your current password. If you’re having trouble remembering your password, consider using a password manager to securely store your login credentials.

Creating a New, Strong Password

Now that you’ve verified your identity, you can create a new password for your Gmail account. It’s crucial to choose a strong, unique password that is difficult for hackers to guess. Here are some tips for creating a strong password:

- Use a combination of uppercase and lowercase letters: Mixing uppercase and lowercase letters makes your password more complex and harder to crack.

- Include numbers and symbols: Adding numbers and symbols to your password significantly increases its strength.

- Make it at least 12 characters long: The longer your password, the more secure it is. Aim for a password that is at least 12 characters long.

- Avoid using personal information: Don’t use your name, birthday, or other easily guessable information in your password.

- Don’t use common words or phrases: Hackers often use dictionaries of common words and phrases to crack passwords. Avoid using these in your password.

- Use a password manager: A password manager can help you generate and store strong, unique passwords for all of your online accounts.

Here are some examples of strong passwords:

P@sswOrd123!MyS3cur3P@sswOrdStr0ngP@sswOrd!

Remember to choose a password that you can remember, but that is also difficult for others to guess. Consider using a mnemonic or a phrase that you can easily recall.

Confirming Your New Password

After creating your new password, you’ll need to confirm it to ensure that you’ve entered it correctly. Here’s how:

- Enter your new password in the “New password” field: Type your new password in the “New password” field.

- Enter your new password again in the “Confirm new password” field: Type your new password again in the “Confirm new password” field. Make sure that the two passwords match exactly.

- Click “Change Password”: Once you’ve confirmed your new password, click the “Change Password” button.

If the two passwords don’t match, you’ll see an error message. Double-check that you’ve entered the passwords correctly and try again. If you’re still having trouble, consider using a password manager to generate and store your password.

Verifying the Password Change

After you’ve changed your Gmail password, it’s a good idea to verify that the change was successful. Here’s how:

- Sign out of your Gmail account: Click on your profile picture or initial in the top right corner of the screen and select “Sign out.”

- Sign back in with your new password: Go to mail.google.com and enter your email address and your new password.

If you’re able to sign in with your new password, then the password change was successful. If you’re having trouble signing in, double-check that you’ve entered the correct password. If you’ve forgotten your new password, you’ll need to go through the password recovery process.

Updating Your Password on Other Devices

Once you’ve changed your Gmail password, it’s important to update your password on all of your other devices, including your smartphone, tablet, and computer. Here’s how to do it:

- On your smartphone or tablet: Go to the settings app and find the “Accounts” or “Passwords & Accounts” section. Select your Google account and update your password.

- On your computer: If you’re using a desktop email client like Outlook or Thunderbird, you’ll need to update your password in the account settings.

If you’re using two-factor authentication, you may also need to generate a new app password for each device or application that you use to access your Gmail account. This is a security measure to ensure that only authorized devices and applications can access your account.

Best Practices for Password Management

Changing your Gmail password is just one step in maintaining your online security. Here are some best practices for password management that you should follow:

- Use a password manager: A password manager can help you generate and store strong, unique passwords for all of your online accounts.

- Enable two-factor authentication: Two-factor authentication adds an extra layer of security to your account by requiring a second verification method, such as a code sent to your phone, in addition to your password.

- Be wary of phishing scams: Phishing scams are emails or websites that try to trick you into giving up your personal information, such as your password. Be careful about clicking on links in emails or entering your password on unfamiliar websites.

- Keep your software up to date: Keeping your operating system, web browser, and other software up to date can help protect you from security vulnerabilities that hackers can exploit.

- Monitor your account activity: Regularly check your Gmail account activity to see if there are any suspicious logins or other unusual activity.

Additional Security Measures for Your Gmail Account

In addition to changing your password and following best practices for password management, there are several other security measures you can implement to fortify your Gmail account against unauthorized access.

Two-Factor Authentication (2FA)

As mentioned earlier, enabling two-factor authentication (2FA) is one of the most effective ways to protect your Gmail account. With 2FA enabled, even if someone manages to obtain your password, they won’t be able to access your account without the second verification method, such as a code sent to your phone or a security key.

To enable 2FA on your Gmail account:

- Go to your Google Account settings.

- Navigate to the “Security” section.

- Under the “Signing in to Google” section, select “2-Step Verification.”

- Follow the on-screen instructions to set up 2FA.

You can choose from several 2FA methods, including:

- Google Prompt: A notification sent to your smartphone that you can approve or deny.

- Authenticator app: An app that generates a unique code every 30 seconds.

- Security key: A physical device that you plug into your computer to verify your identity.

- Backup codes: A set of one-time-use codes that you can use if you don’t have access to your primary 2FA method.

Reviewing Account Activity

Regularly reviewing your Gmail account activity can help you identify any suspicious logins or other unusual activity. To review your account activity:

- Go to your Google Account settings.

- Navigate to the “Security” section.

- Under the “Recent security activity” section, select “Review security events.”

This will show you a list of recent logins to your account, including the date, time, location, and device used. If you see any logins that you don’t recognize, it’s possible that your account has been compromised. In this case, you should immediately change your password and enable 2FA.

Managing Third-Party Access

Many third-party apps and services request access to your Gmail account. While some of these apps are legitimate, others may be malicious. It’s important to carefully review the permissions that you grant to third-party apps and services and revoke access to any apps that you no longer use or trust.

To manage third-party access to your Gmail account:

- Go to your Google Account settings.

- Navigate to the “Security” section.

- Under the “Third-party apps with account access” section, select “Manage third-party access.”

This will show you a list of all the third-party apps and services that have access to your Gmail account. You can revoke access to any app by clicking on it and selecting “Remove Access.”

Setting Up Recovery Options

If you ever forget your password or lose access to your account, having recovery options in place can help you regain access quickly and easily. Google offers several recovery options, including:

- Recovery email address: An alternate email address that Google can use to send you a password reset link.

- Recovery phone number: A phone number that Google can use to send you a verification code.

- Security questions: Questions that only you know the answer to.

To set up recovery options for your Gmail account:

- Go to your Google Account settings.

- Navigate to the “Personal info” section.

- Under the “Contact info” section, select “Email” or “Phone.”

- Follow the on-screen instructions to add a recovery email address or phone number.

- Under the “Security” section, select “Recovery questions” to set up security questions.

Make sure to keep your recovery options up to date, as they can be crucial in regaining access to your account if you ever lose your password.

Conclusion: Staying Secure in the Digital Age

Changing your Gmail password with your old password is a simple yet essential step in maintaining your online security. By following the steps outlined in this guide, you can ensure that your Gmail account remains secure and accessible. Remember to choose a strong, unique password, update your password on all of your devices, and follow best practices for password management. Additionally, consider implementing additional security measures such as two-factor authentication, reviewing account activity, managing third-party access, and setting up recovery options.

In today’s digital age, online security is more important than ever. By taking proactive steps to protect your Gmail account, you can safeguard your personal information and prevent potential security breaches. Stay vigilant, stay informed, and stay secure.

By implementing these strategies and staying proactive about your account security, you can significantly reduce the risk of your Gmail account being compromised. Remember that maintaining a strong security posture is an ongoing process, and it’s important to regularly review and update your security measures to stay ahead of potential threats. Your digital safety is paramount, and taking these steps will help you navigate the online world with greater confidence and peace of mind.